计算机体系结构分类

CISC与RISC

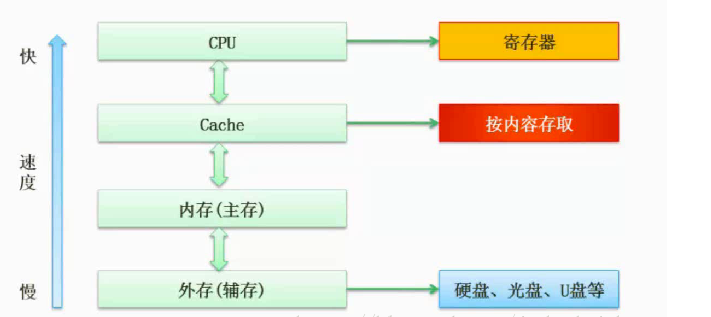

层次化存储结构

Cache - 概念

Cache的功能:提高CPU数据输入输出的速率,突破冯·诺依曼瓶颈即CPU与存储系统间数据传关带宽限制。

在计算机的存储系统体系,Cache是访问速度最快的层次。

使用Cache改善系统性能的依据是程序的局部性原理

如果以h代表Cache的访问命中率,t1表表Cache的周期时间,t2表示主存储器周期时,以读操作为例,使用“Cache+主存储器”的统平均周期为t3.则:其中(1-h)又称为失效率(未命中率)

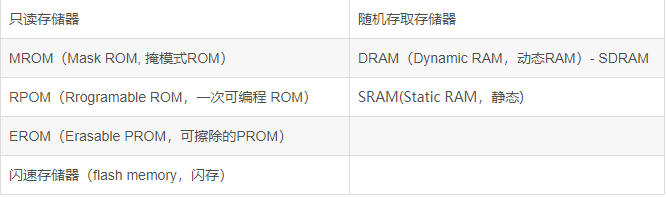

主存-分类

指令

计算机执行指令的过程分为如下几个步骤。

(1) 取指令。控制器首先按程序计数器所指出的指令地址从内存中取出一条指令。

(2) 指令译码。将指令的操作码部分送指令译码器进行分析,然后根据指令的功能向有关部件发出控制命令。

(3) 按指令操作码执行。根据指令译码器分析指令产生的操作控制命令以及程序状态字(PSW) 寄存器的状态,控制微操作形成部件产生一系列CPU内部的控制信号和输出到CPU外部控制信号。在这一系列控制信号的控制下,实现指令的具体功能。

(4) 形成下一条指令地址。若非转移类指令,则修改程序计数器的内容;若是直接转移类指令,则该指令中的转移地址被送入程序计数器:若是非直接转移类指令,则根据转移条件修改程序计数器的内容。

指令系统的优化设计向着两个方向发展:复杂指令系统计算机(CISC)和精简指令系统计算机(RISC)

CISC (Complex Instruction Set Computer,复杂指令集计算机)的基本思想是进一步增强原有指令的功能,用更为复杂的新指令取代原先由软件子程序完成的功能,实现软件功能的硬件化,导致机器的指令系统越来越庞大而复杂。CISC计算机一般所含的指令数目至少300条以上,有的甚至超过500条。

CISC的主要缺点如下:①微程序技术是CISC的重要支柱,每条复杂指令都要通过执行一段解释性微程序才能完成,这就需要多个CPU周期,从而降低了机器的处理速度;②指令系统过分庞大,从而使高级语言编译程序选择目标指令的范围很大,并使编译程序本身冗长而复杂,从而难以优化编译使之生成真正髙效的目标代码:③CISC强调完善的中断控制,势必导致动作繁多,设计复杂,研制周期长:④CISC给芯片设计带来很多困难,使芯片种类增多,出错几率增大,成本提高而成品率降低。

RISC (Reduced Instruction Set Computer,精简指令集计算机)的基本思想是通过减少指令总数和简化指令功能,降低硬件设计的复杂度,使指令能单周期执行,并通过优化编译,提高指令的执行速度,采用硬线控制逻辑,优化编译程序。

实现RISC的关键技术有:①重叠寄存器窗口(overlapping register windows)技术,首先应用在伯克利的RISC项目中;②优化编译技术,RISC使用了大量的寄存器,如何合理分配寄存器、提高寄存器的使用效率,减少访存次数等,都应通过编译技术的优化来实现;③超流水及超标量技术,这是RISC为了进一步提高流水线速度而采用的新技术;④硬线逻辑与微程序相结合在微程序技术中。

嵌入式处理器

嵌入式处理器是嵌入式系统的核心部件,一般可分为嵌入式微处理器(MPU)、微控制器(MCU)、数字信号处理器(DSP)和片上系统(SOC)

MPU采用增强型通用微处理器,由于嵌入式系统通常应用于环境比较恶劣的环境中,因而MPU在工作温度、电磁兼容性以及可靠性方面的要求较通用的标准微处理器高。但是,MPU在功能方面与标准的微处理器基本上是一样的。 MCU又称单片微型计算机(Single Chip Microcomputer)或者单片机,是指随着大规模集成电路的出现及其发展,将计算机的CPU、RAM、ROM、定时计数器和多种I/O接口集成在一片芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。DSP是一种独特的微处理器,是以数字信号来处理大量信息的器件。实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,它的强大数据处理能力和高运行速度,是最值得称道的两大特色。SOC称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。

总线

总线是一组能够为多个部件分时共享的公共信息传送线路。分时是指同一时间只能允许一个部件向总线发送信息。然而,同一时间,允许多个部件接收相同的信息。包括地址总线、数据总线、控制总线。

总线是一组能为多个部件分时共享的信息传送线,用来连接多个部件并为之提供信息交换通路。所谓共享,指连接到总线上的所有部件都可通过它传递信息;分时性指某一时刻只允许一个部件将数据发送到总线上。因此,共享是通过分时实现的。

CPU访问内存通常是同步方式,CPU与I/O接口交换信息通常是同步方式,CPU与PCI总线交换信息通常是同步方式,I/O接口与打印机交换信息则通常采用基于缓存池的异步方式。

虚拟存储器

虚拟存储器是一个容量非常大的存储器的逻辑模型,不是任何实际的物理存储器。

它借助于磁盘等辅助存储器来扩大主存容量,使之为更大或更多的程序所使用。虚拟存储器管理方式分为页式虚拟存储器、段式虚拟存储器和段页式虚拟存储器。

虚拟存储器是由硬件和操作系统自动实现存储信息调度和管理的。它的工作过程包括6个步骤:

①中央处理器访问主存的逻辑地址分解成组号a和组内地址b,并对组号a进行地址变换,即将逻辑组号a作为索引,查地址变换表,以确定该组信息是否存放在主存内。

②如该组号已在主存内,则转而执行④;如果该组号不在主存内,则检查主存中是否有空闲区,如果没有,便将某个暂时不用的组调出送往辅存,以便将需要访问的信息调入主存。

③从辅存读出所要的组,并送到主存空闲区,然后将那个空闲的物理组号a和逻辑组号a登录在地址变换表中。

④从地址变换表读出与逻辑组号a对应的物理组号a。

⑤从物理组号a和组内字节地址b得到物理地址。

⑥根据物理地址从主存中存取必要的信息。

页式调度是将逻辑和物理地址空间都分成固定大小的页。主存按页顺序编号,而每个独立编址的程序空间有自己的页号顺序,通过调度,辅存中程序的各页可以离散装入主存中不同的页面位置,并可据页表一一对应检索。

内存地址字节算法

内存按字节编址,地址从A4000H到CBFFFH,共有 (1) 个字节。若用存储容量为32K×8bit的存储芯片构成该内存,至少需要 (2) 片。

(1)A.80K B.96K C.160K D.192K

(2)A.2 B.5 C.8 D.10

试题解析:CBFFFH - A4000H + 1 = 28000H = 160K。160K / 32K = 5。答案:(1)C (2)B

A4000H和CBFFFH都是表示十六进制的数据,H表示的就是十六进制,所以A4000H到CBFFFH共有的字节数为:CBFFFH(835583)-A4000H(671744)+1=28000H(163840),些等式中尾数为H的表示十六进制数,而括号中的数是其相应的十进制数,所以它们中间共有163840个字节,而163840/1024=160,从而得出A4000H到CBFFFH中共有160*1024个字节。

地址编号A0000H到DFFFFH的内存空间为DFFFFH-A0000H+1=40000H个若内存按字节编址,即每个空间存储一个字节则地址编号A0000H到DFFFFH的内存空间的存储容量为40000H*8比特。

用存储容量为32K*8比特的存储芯片构成地址编号A0000H到DFFFFH的内存空间,则至少需要40000H*8比特/32K*8比特=40000H/8000H=5片

`